Draw Hdl Design Flow And Explain

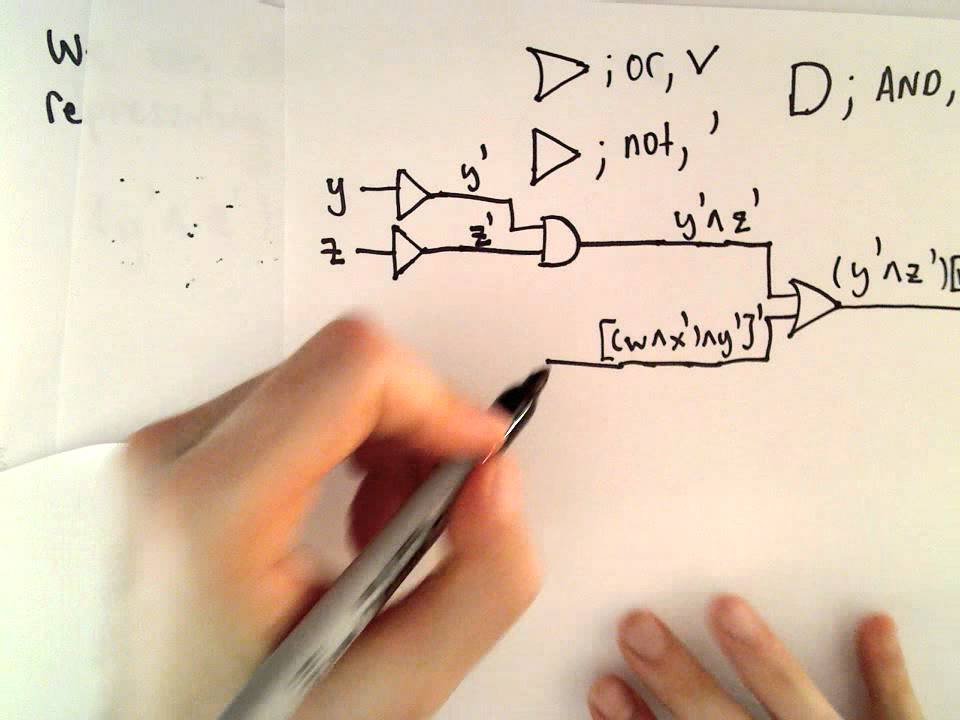

In computer engineering a hardware description language hdl is a specialized computer language used to describe the structure and behavior of electronic circuits and most commonly digital logic circuits.

Draw hdl design flow and explain. This description is called register transfer level rtl description. The chip design includes different types of processing steps to finish the entire flow. Flow to hdl tools and methods convert flow based system design into a hardware description language hdl such as vhdl or verilog. Verilog hdl was designed by phil moorby who was later to become the chief designer for verilog xl and the first corporate fellow at cadence design systems.

There are different types of design procedures for analog digital designs and fpga designs. 1 draw the design flow of vhdl and explain each block. These steps are applicable to any hdl based design process. To create a design we write hardware description language hdl which is of two types verilog and vhdl.

Fpga design flow in this part of tutorial we are going to have a short intro on fpga design flow. Design module of 3 bit full adder using full adder 4. Fpga design flow design entry there are different techniques for design entry. Large logic designs like software programs are hierarchical and.

Design module of quadruple 2 to 1 line multiplexer 5. Although the design flow is drawn as a waterfall diagram with flow only in a downward direction it is in fact an iterative process in which the designer can return to or redo any step until the proper functionality is arrived at. A hardware description language enables a precise formal description of an electronic circuit that allows for the automated analysis and simulation of an electronic circuit. Design module of full adder using half adder 3.

In this step the control flow word widths register allocation arithmetic operations and logic operations of the design that represent the functional design are derived and tested. For anyone who just started his carrier as a vlsi engineer has to understand all the steps of the vlsi design flow to become good in his area of operations. Then the hdl is synthesized into a bit file using a bitgen to configure the fpga. Rtl is expressed in a hardware description language hdl such as vhdl or.

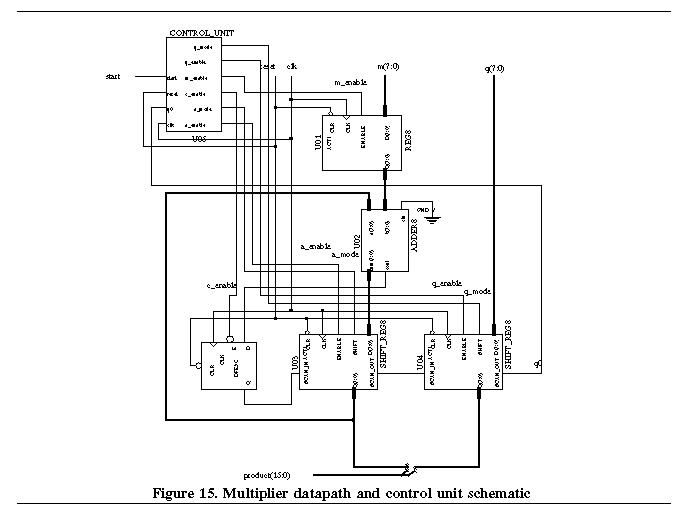

Design flow there are several steps in an hdl based design process often called the design flow. A simplified version of design flow is given in the flowing diagram. The so called front end begins with figuring out the basic approach and building blocks at the block diagram level. The design flow described in this document consists of five major procedures as shown in figure 1 functional design synthesis place route system integration and fabrication.

The company was privately held at that time by dr. Design module of half adder 2. The fpga stores the configuration in ram that is the configuration is lost when there is no power connectivity. Design module of the custom adder circuit 6.

Prabhu goel the inventor of the podem test generation algorithm. Typically this is a method of creating designs for field programmable gate array application specific integrated circuit prototyping and digital signal processing dsp design.